Today’s embedded applications are extremely complex with a single microcontroller handling multiple functions. These applications demand enhanced safety and optimal execution time with real-time response, along with seamlessly synchronizing various functions. From motor control with integrated power factor correction to handling light intensity, complex applications require switching among various modules with ease. Processor driven timing and sequencing solutions are subject to inherent latencies, which cannot always be accurately predicted. This approach also consumes precious CPU bandwidth, under-utilizing its capabilities, which could be off-loaded to optimize the application performance. The Peripheral Trigger Generator (PTG), a Core Independent Peripheral (CIP), featured in Microchip’s 16-bit dsPIC33 Digital Signal Controller (DSC) devices, enables precise timing and sequencing of functions in complex applications to be coordinated, while off-loading the CPU. Several examples are detailed to showcase how the PTG helps to streamline peripheral sequencing for timing-critical applications such as controlling a motor with power factor correction, controlling the intensity of light or generating a constant frequency signal which also acts as a clock source independent from the core. Since the PTG is core independent, this work can be done while the CPU sleeps to save power or focuses on other critical tasks.

Today’s embedded applications are extremely complex with a single microcontroller handling multiple functions. These applications demand enhanced safety and optimal execution time with real-time response, along with seamlessly synchronizing various functions. From motor control with integrated power factor correction to handling light intensity, complex applications require switching among various modules with ease. Processor driven timing and sequencing solutions are subject to inherent latencies, which cannot always be accurately predicted. This approach also consumes precious CPU bandwidth, under-utilizing its capabilities, which could be off-loaded to optimize the application performance. The Peripheral Trigger Generator (PTG), a Core Independent Peripheral (CIP), featured in Microchip’s 16-bit dsPIC33 Digital Signal Controller (DSC) devices, enables precise timing and sequencing of functions in complex applications to be coordinated, while off-loading the CPU. Several examples are detailed to showcase how the PTG helps to streamline peripheral sequencing for timing-critical applications such as controlling a motor with power factor correction, controlling the intensity of light or generating a constant frequency signal which also acts as a clock source independent from the core. Since the PTG is core independent, this work can be done while the CPU sleeps to save power or focuses on other critical tasks.

As the name suggests, the PTG is a user-programmable sequencer that generates triggers with complex input signal sequences to coordinate the operation of other on-chip peripherals. Applications that use the PTG do so with other peripherals, such as an Analog-to-Digital Converter (ADC), Output Compare (OC), Pulse-Width Modulator (PWM), timers and interrupt controllers to achieve a complex sequence of triggers and responses. The PTG not only reduces the application dependency on the core but also solely takes care of module interactions, which helps to reduce software complexity and maintain modularity.

The PTG peripheral supports 8-bit commands, called the step commands, to the PTG queue registers. Each 8-bit step command is comprised of a 4-bit command code and a 4-bit option field. These commands define a sequence of events for generating output trigger signals to the peripherals. The step commands can also be used to generate interrupt requests to the core.

Power factor and motor control

In an integrated Power Factor Correction (PFC) and motor control application, a single DSC controls a permanent magnet synchronous motor using a Field Oriented Control (FOC) scheme as well as the PFC converter. This application requires three PWM channels to control the motor functioning and an additional PWM to control the PFC operation. An Output Compare (OC) peripheral can be used to augment the number of PWM channels available to the application, even beyond the number of high-speed PWM channels available on the device.

The PWM peripheral together with an OC peripheral, can be used to generate the necessary signals for motor control and PFC operation. However, in an application such as PFC, execution timing is very important making it necessary to complete various tasks within an optimal execution time. These include synchronising motor control and PFC PWM, triggering ADC for conversion and switching ADC channels used for motor control and PFC feedback signals.

These requirements can be achieved effectively using the PTG peripheral, which can synchronise the high-speed PWM and OC peripherals and generate ADC peripheral triggers by monitoring high-speed PWM peripheral edges. It also monitors the “ADC conversion done” interrupt and generates appropriate interrupts, executing the FOC and digital PFC control code. And it reduces CPU intervention, making the peripheral handling core independent. This reduces the overall power consumption of your application while freeing up the CPU to perform more critical functions. The switching frequency of motor control and PFC PWM should be selected such that it is in integral multiples.

The ADC in the dsPIC® DSC is capable of four-channel simultaneous sampling. Both FOC and PFC algorithms have their own analog channels that need to be sampled simultaneously, because the phase relationship of these signals is key to implementing efficient control.

The feedback signals of the motor control and PFC should be selected such that, by alternating between the ADC channel selections, both motor control and PFC signals are sampled. The motor control and PFC signals can be connected to the sample-and-hold (S&H) circuits before triggering the ADC, based on the edges of the PWM. The channels should be configured in such a way that, at the end of a four-channel sample and conversion sequence, the conversion results for either FOC or PFC are available in their corresponding ADC buffer registers.

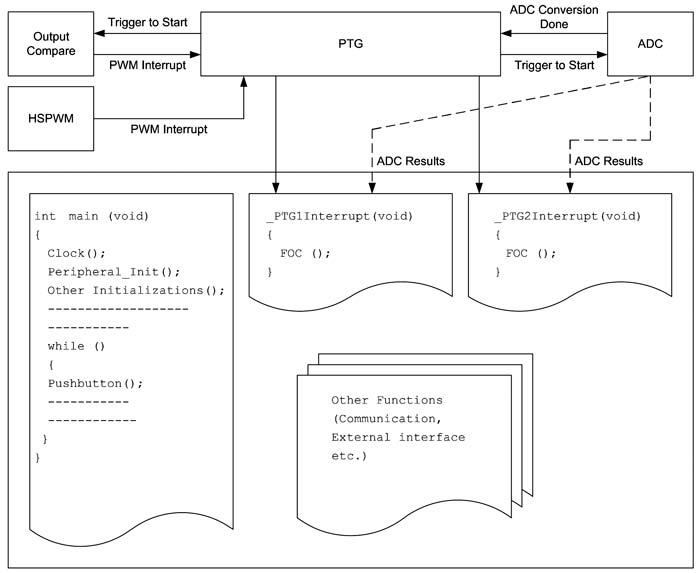

After setting the channel selection bits to connect the PFC feedback signals to the S&H circuit of an ADC, for every PFC PWM cycle, a trigger has to be generated. Similarly, for every motor control PWM cycle, an ADC trigger has to be generated after setting the channel selection bits to connect the motor control feedback signals to the S&H circuit of the ADC. Hence, the PTG peripheral is configured to generate an ADC trigger by monitoring the edges of the motor control and PFC PWM pulses. In addition, two PTG interrupts are generated to execute the code for FOC and PFC, as shown in Figure 1.

As seen in this example, a PTG simplifies the implementation by efficiently sequencing the use of the ADC and PWMs to achieve motor control and PFC implementation in one dsPIC33 device.

Lighting control

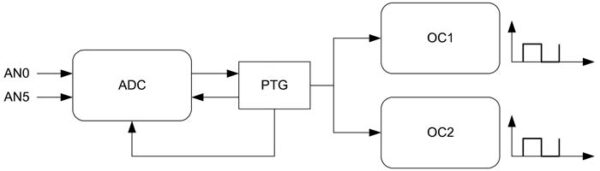

In a light intensity control application, a PWM generator using an OC can be used to control the brightness of a light.

In this application, two OC peripherals are used and their duty cycles are controlled by inputs obtained from two separate ADC channels. Depending on each ADC value, the duty cycle is updated. The PTG peripheral supports a simpler way of synchronising ADC and OC peripherals. In addition, the PTG helps avoid a peripheral deadlock to enhance application safety.

To perform synchronisation, the circuit first monitors the ADC and generates appropriate interrupts to change the OC duty cycle. It then changes the ADC channel without disturbing the CPU, as the PTG can do this independently. As an additional safety feature, in the event of an unexpected failure, the PTG peripheral has a dedicated watchdog timer to monitor and perform the necessary required corrective actions.

A block diagram of this application is shown in Figure 2.

The watchdog timer within the PTG peripheral will prevent a situation where the PTG waits indefinitely for an external event when executing a command that waits for a hardware trigger high-low state. In this application, the PTG will wait for an ADC-conversion-done trigger. Once enabled, the watchdog timer starts counting when the command execution starts. It is disabled when the command completes execution. If an expected event fails to arrive before the watchdog timer time-out period expires, the PTG peripheral aborts the failing command underway and halts the sequencer. It then issues a watchdog timer error interrupt to the CPU.

This acts as a safety feature to recover from a situation where the ADC or PTG peripheral stops working. These peripherals can be re-initialized and restarted within the watchdog timer error interrupt.

The PTG will make the application core independent by switching the ADC channels and monitoring peripherals without the CPU peripheral’s intervention. This enables the CPU to be used for other tasks in the application.

The PTG alone will take care of all interactions within a peripheral, which helps reduce software complexity and maintain modularity. The PTG peripheral’s watchdog timer will help recover from any catastrophic failure, thereby providing a more robust application.

Constant frequency waveform

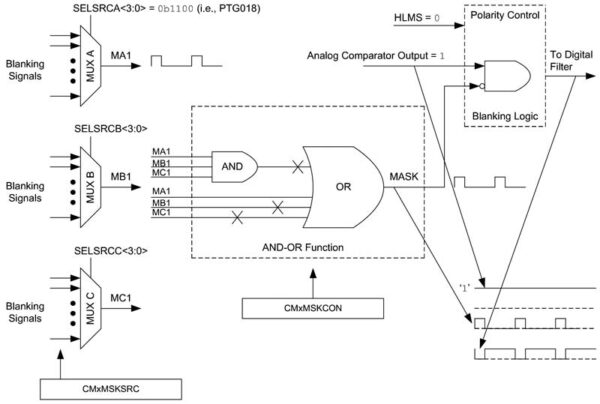

A PTG peripheral can be used to generate a constant frequency signal which also acts as a clock source. The PTG triggers a comparator which acts as a mask input select. The PTG’s trigger pulse width can be varied and the PTG has its own timer. The peripheral trigger can also work as a mask input select for the op amp and comparator, as shown in Figure 3.

Using this feature, a PTG output can be brought out through a comparator peripheral. The comparator is configured such that the inverting input is connected to ground and the non-inverting input is connected to an internal reference voltage.

The trigger pulse will directly emerge as the comparator output. As long as the PTG generates triggers continuously, the comparator will generate a constant frequency waveform. The pulse width of the waveform will be one cycle of the PTG clock.

The on-off times can be controlled by the PTG timer and pulse-width bits. The output pulse width will decide the off time of the output waveform and the timer will decide the on-time of the output waveform, which is the delay between the triggering comparator peripherals.

Depending on the comparator output polarity, the on-off time will be controlled by either the timer or pulse-width bits. The output frequency can also be controlled by a register that acts as a clock divider.

By changing the comparator output polarity, a complementary waveform can be generated using four comparator peripherals. The width of the pulse can be modified using the pulse-width bits, which reduce the frequency of the output. Hence, a constant waveform can be generated using the PTG and comparator peripherals.

Among the advantages of using the PTG in this application are that the output can act as a constant clock source and run completely independent of the core. Using more comparator peripherals, an even complementary waveform can be generated. The PTG also works in power-saving modes such as idle and sleep.

Summary

The PTG peripheral in Microchip’s dsPIC33 Digital Signal Controller devices lets users design complex application sequences with increased flexibility for timing-critical or power-critical applications. A PTG allows various peripherals to interact with each other with little to no CPU interruption and enhances the capabilities of the existing peripherals, thus expanding the possibilities of what any given peripheral can accomplish.

Using a PTG peripheral provides faster response time and reduced software burden. The peripheral also provides built-in functions, such as a dedicated watchdog timer, that increase functional safety.

Additional resources: Applications of the Peripheral Trigger Generator (PTG) Application Note: http://ww1.microchip.com/downloads/cn/AppNotes/cn586398.pdf

Author: Ravikiran Shetty,

Applications Engineer

Microchip Technology | https://www.microchip.com