Imperas Software Ltd., the leader in RISC-V simulation solutions, today announced the latest updates to ImperasDV to support the rapid growth in RISC-V verification as developers extend into established and emerging applications with new design innovations based on the flexibility of RISC-V. ImperasDV is the integrated solution for RISC-V processor verification that supports both RTL bug detection and analysis, when combined with design flow integration for the leading EDA SystemVerilog environments with Cadence, Siemens EDA, and Synopsys.

Imperas Software Ltd., the leader in RISC-V simulation solutions, today announced the latest updates to ImperasDV to support the rapid growth in RISC-V verification as developers extend into established and emerging applications with new design innovations based on the flexibility of RISC-V. ImperasDV is the integrated solution for RISC-V processor verification that supports both RTL bug detection and analysis, when combined with design flow integration for the leading EDA SystemVerilog environments with Cadence, Siemens EDA, and Synopsys.

Verification IP – SystemVerilog Functional coverage library: riscvISACOV

Design Verification (DV) teams use coverage analysis as the key metric for progress toward the completion of verification plans. For the open standard specification of RISC-V, a coverage library can be configured based just on the specification definition. However, since a processor has many complex states due to privilege modes, interrupts and dynamic effects, the coverage library needs to consider the complete operational behaviour of a processor, not just a block-level functional unit. The ImperasDV Verification IP options have been extended to include riscvISACOV, a set of SystemVerilog source functional coverage libraries for all of the ratified instruction extensions and the first release of the privilege mode libraries to be used in conjunction with the effects of asynchronous events during verification. See https://github.com/riscv-verification/riscvISACOV for more information and to download.

Verification IP – Test suites

The latest ImperasDV updates include architectural validation test suites that are important for RISC‑V developers to ensure hardware implementations are in line with the expectations of the software ecosystem supporting RISC-V. The ImperasDV Verification IP options have been extended to include architectural validation test suites for RV32E, RV64E, Zc, and Zmmul specifications. See https://github.com/riscv-ovpsim/imperas-riscv-tests for more information and to download.

RISC-V implications for SoC Verification

Current SoC Design Verification (DV) methodologies are based on established standards such as UVM (Universal Verification Methodology) and test benches implemented in SystemVerilog. However, SoC verification is traditionally based on the principle of ‘known good’ processor IP cores from a mainstream supplier. RISC-V is an open standard ISA (Instruction Set Architecture) with the potential for developers to design an optimized processor for a target application and yet retain the key compatibility to leverage the software ecosystem. Verification of a RISC-V processor at the point of use represents the biggest shift in verification responsibility in a generation. With the design flexibility of RISC-V, all adopters that choose to explore these new design freedoms will also need to face the challenge of high-quality processor verification.

RISC-V Verification

As an open standard ISA, RISC-V is a natural option for developers looking to optimize a processor for both traditional and emerging applications. The RISC-V specifications are based on a modular framework with many standard extensions, each with significant options and configuration flexibility. All the design flexibility of RISC-V increases the requirements for extensive verification plans, including full dynamic operations with asynchronous events and debug modes of operation. This new trend highlights the industry-wide need for standards and methodologies that can support the growing RISC-V Verification Ecosystem.

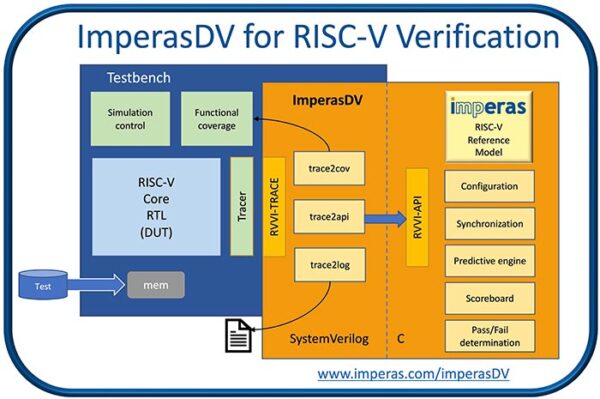

RVVI (RISC-V Verification Interface)

To help leverage the investment in verification IP and test infrastructure, the new open standard RVVI (RISC-V Verification Interface) has been adopted by many commercial developers and open-source projects such as the OpenHW projects with the roadmap of CORE-V IP cores. RVVI provides a common methodology for the key components of the testbench to connect the RTL instruction trace and reference models to fully support the ‘lock-step-compare’ verification approach. The RVVI flexibility supports the full range of RISC-V specifications and features and can be adopted with increasing levels of capability for designs with privilege modes, vector extensions, out-of-order pipelines, multi-threading, multi-hart, multi-issue, plus user-defined custom instructions and extensions. RVVI supports the innovation of RISC-V with the flexibility required for verification IP and reuse as DV teams scale up to support the rapid growth in RISC-V verification projects. See https://github.com/riscv-verification/RVVI for more information and to download.

“RISC-V offers new freedoms in design flexibility which is driving a new wave of innovation across the semiconductor industry in almost all market segments,” said Larry Lapides, VP of Sales at Imperas Software Ltd. “This is creating a resurgence in teams exploring custom processors with domain-specific optimized features, and as they take up the challenge of RISC-V processor verification, we are experiencing a massive shift in momentum as both new and established development teams invest massive amounts of time, energy and resources into processor verification. Verification is becoming a golden opportunity for quality tools providers addressing the needs of RISC-V development teams.”

“Through the dedicated efforts of the specialist verification teams, with standards such as UVM and SystemVerilog, SoC verification is now a ‘solved-problem’,” said Simon Davidmann, CEO at Imperas Software Ltd. “As SoC developers embrace the freedoms of RISC-V, verification solutions and methodologies based on the established flows with UVM and SystemVerilog are allowing SoC DV teams to scale up to the complexities of RISC-V processor verification. ImperasDV provides the path from the established SoC techniques into the new challenges of RISC-V verification. A clear must-have for any solution is a complete design flow with full compatibility with the big 3 EDA environments to maintain the efficiency and throughput as the industry brings ever more complex designs to market without delay.”