Today’s engineers are often challenged to develop increasingly sophisticated designs while completing them within shorter schedules. The requirements for products that include additional functional safety features or complex communications capabilities adds to the design complexity and challenges. Sometimes compounding these challenges is the geographically-dispersed nature of the engineers available to work on a particular product. For example, a contemporary automotive DC to DC converter design project team might be comprised of power supply firmware developers from one site or country and communication stack firmware developers from another site or country. Integrating the code developed at multiple locations onto the same microcontroller can increase the schedule risk due to the complex interaction between the separately designed firmware.

Today’s engineers are often challenged to develop increasingly sophisticated designs while completing them within shorter schedules. The requirements for products that include additional functional safety features or complex communications capabilities adds to the design complexity and challenges. Sometimes compounding these challenges is the geographically-dispersed nature of the engineers available to work on a particular product. For example, a contemporary automotive DC to DC converter design project team might be comprised of power supply firmware developers from one site or country and communication stack firmware developers from another site or country. Integrating the code developed at multiple locations onto the same microcontroller can increase the schedule risk due to the complex interaction between the separately designed firmware.

Introducing the Dual-core DSC family

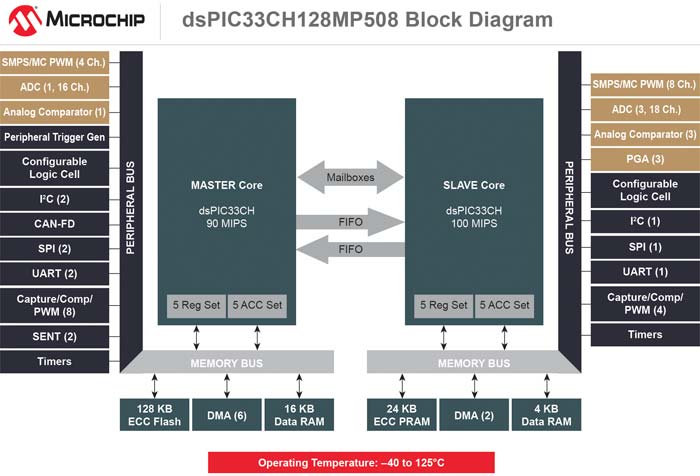

System developers designing high-end embedded control applications with multiple software teams can now benefit from a new family of dual-core Digital Signal Controllers (DSCs) in a single chip, enabling easier software integration. Microchip Technology’s dsPIC33CH has one core designed to function as a master, while the other functions as a slave. In this master-slave architecture, the slave core can be used for executing dedicated, time-critical control code, while the master core is busy running system-level functions, including user interface (UI), monitoring and communications, customised for the end application.

The dsPIC33CH is designed to facilitate independent code development for each core by separate design teams – but later enables seamless integration when they are brought together in one chip. Its dual independent cores simplify firmware development, enabling a multi-team software development approach, with two workflows running in parallel. Time-critical control loops can be separated from housekeeping functions such as UI, monitoring and diagnostics, and communication. This speeds the development process, allows each core’s code to be individually and more effectively optimised, with minimal code interaction between the two cores, easing the debug process.

Ideal Applications

The dsPIC33CH family is optimised for high-performance digital power, motor control and embedded applications requiring sophisticated algorithms. Typical power applications for this dual-core controller include wireless charging, server power supplies, DC to DC converters, chargers and inverters. The family will also be popular for motor control in pumps, fans, drones, robotics, power tools and consumer appliances. As a high-performance DSC, these devices excel when used in automotive electronic sensors, industrial automation and control and medical diagnostic equipment. Benefiting from two microcontroller cores on the same die, this family can provide the performance required for gateways and central processors for IoT applications.

For example, in a digital power supply, the slave core manages the math-intensive algorithms, closing the control loop in firmware by running latency-critical compensator algorithms, while the master core independently manages the PMBus™ protocol stack and provides system monitoring functions, increasing overall system performance and responsiveness.

For example, in a digital power supply, the slave core manages the math-intensive algorithms, closing the control loop in firmware by running latency-critical compensator algorithms, while the master core independently manages the PMBus™ protocol stack and provides system monitoring functions, increasing overall system performance and responsiveness.

In an automotive fan, pump or other motor control application, the slave core can be dedicated to executing time-critical speed and torque control, while the master core runs functional safety routines and manages the Controller Area Network Flexible Data rate (CAN-FD) stack for robust communications, as well as other system-level functions, including monitoring and diagnostics.

And in other high-performance embedded applications, such as electronic sensors used in automotive or IoT systems, the slave core accelerates math-intensive functions, such as DSP filtering of sensor inputs, while the master core facilitates reliability and fault-tolerance for safety-critical applications.

High-Performance

The master core has 64 to 128 Kilobytes of program flash, with ECC and 16KB RAM, while the slave has 24KB of program RAM, with ECC and 4KB data RAM. Core frequency for the master is 90 MIPS at 180MHz, while the slave delivers 100 MIPS at 200MHz. Additionally, both processor sub-systems have their own interrupt controllers, clock generators, port logic, I/O MUXes and PPS. The device is effectively the equivalent of having two complete dsPIC® DSCs on a single die.

The two cores work seamlessly together, enabling advanced algorithms to improve efficiency and responsiveness. In addition, each of the new cores in dsPIC33CH devices has been designed to deliver more performance than current dsPIC DSC cores, through more context-selected registers to improve interrupt responsiveness, new instructions to accelerate DSP (digital signal processor) performance and faster instruction execution. In a performance-critical calculation used in many power supplies, the new controller achieves core performance almost twice as fast as the previous generation – with latency of 280ns, compared to 543ns.

Another key benefit of distributing processing workload across two DSC cores in a single device is the ability to achieve higher power density through higher switching frequencies (more than 2MHz compared to around 1MHz for a single-core controller), which can result in smaller components.

Live system updates enable firmware to be upgraded with zero downtime, which is especially important in high-availability systems, such as server power supplies. Additionally, the dsPIC33CH architecture allows the two cores to be programmed to monitor each other for functional safety reasons, facilitating robust system design.

To reduce system costs and board size, typical advanced peripherals available to each core include high-speed Analog to Digital Converters (ADCs), Digital to Analog Converters (DACs) with waveform generation, analogue comparators, analogue programmable gain amplifiers and high-resolution Pulse Width Modulation (PWM) with 250 ps resolution. With up to 12 PWM channels, the controller is well suited for uninterruptible power supplies (UPS), DC/DC converters and AC/DC power supplies.

The devices in the dsPIC33CH family are the first Microchip dual core, 16-bit digital signal controllers, and they deliver unprecedented integration in packages as small as 5 x 5 mm. These are the first dsPIC33s capable of managing CAN-FD for robust communication, with increased bandwidth. It is available in eight package variants and is supported by Microchip’s MPLAB® development ecosystem, including Microchip’s free, downloadable and award-winning MPLAB X Integrated Development Environment (IDE) and MPLAB Code Configurator.

Conclusion

Microchip’s dsPIC33CH is optimised for high-performance and time-critical, real-world embedded control applications. The dsPIC33CH family enables separate code design and seamless integration, while also reducing system cost and size.

Author:

Tom Spohrer

Microchip Technology | https://www.microchip.com