PLS Programmierbare Logik & Systeme and HighTec EDV-Systeme present a completely new common development environment for Power Architecture e200 core based SoCs from STMicroelectronics and Freescale at electronica 2010 in Hall A6, Booth A6.442 (PLS) and Booth A6.S04 (HighTec).

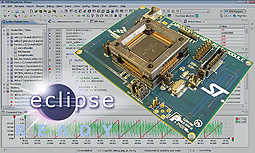

Key elements of the ‘Power Architecture Development Platform’, developed both for automotive and for demanding industrial applications, are the GNU technology based compiler from HighTec and the Universal Debug Engine (UDE) from PLS, which thanks to an own Eclipse perspective offers users cross debugger functionality, without any restrictions, in an Eclipse based development environment.

The GNU compiler can generate both standard PowerPC instructions and Variable Length Encoding (VLE) instructions that are important for Power Architecture based SoCs. The latter ensure a high code density. Since the development environment automatically selects the corresponding startup code, the necessary hardware initialization, the memory mapping as well as the right peripheral specific header file supplied, own or sample applications for all microcontrollers of the SPC56 family from STMicroelectronics and the MPC55xx and MPC56XX families from Freescale can be generated in Eclipse. With the appropriately prepared target configuration files, these applications can be run immediately on the respective evaluation boards of the manufacturer.

The Eclipse perspective of the Universal Debug Engine (UDE) supports the GNU compiler with a number of debug functions that go far beyond the standard scope of the C/C++ Development Tooling (CDT) from Eclipse. The most important functions include, for example, continuous updating of target data in the debugger window even when a program is running, presentation of the extensive peripheral registers in textual or symbolic form as well as the visualization of trace data. Furthermore, the UDE perspective also allows the control of several debugger instances and thereby unrestricted multicore debugging.

The UDE is complemented with the powerful Universal Access Device family (UAD2+/UAD3+) from PLS, which extensively supports both debugging via a JTAG interface and the Nexus port that is nowadays typically used for program and data trace. With the UAD3+ up to 4 GB of memory are available for trace recording, whereby the recorded data from the UDE software are not only used to display the program flow, but also for system debugging functions such as code coverage and profiling measurements. Moreover, transfer rates of up to 1 MByte/s via JTAG not only ensure a fast flash programming, but also short turn-around times during development.