Renesas Electronics Corporation, a premier supplier of advanced semiconductor solutions, announced the release of IP Utilities – a new series of solutions aimed at simplifying the development of devices incorporating Renesas intellectual property (IP). The new IP Utilities include application packages and evaluation kits, as well as expanding Renesas’ growing portfolio of leading-edge IP licenses.

Renesas Electronics Corporation, a premier supplier of advanced semiconductor solutions, announced the release of IP Utilities – a new series of solutions aimed at simplifying the development of devices incorporating Renesas intellectual property (IP). The new IP Utilities include application packages and evaluation kits, as well as expanding Renesas’ growing portfolio of leading-edge IP licenses.

With the emergence of CPUs based on open-source architectures such as RISC-V, the use of licensed IP for device development is becoming more attractive from the cost, time and design risk perspectives. Developing original devices has become very demanding in terms of both the growing number of steps and the time required, due to the need to verify many IP component combinations, such as peripheral functions and application-specific functions. Leveraging Renesas’ extensive manufacturing expertise and the new IP Utilities solutions, developers can confidently shorten the development time for their original semiconductor devices based on Renesas’ highly reliable IP and reduce the time to market.

“Our IP portfolio lineup has grown to include more than 80 offerings since Renesas first entered the IP licensing market in 2018,” said Tetsuya Matsumoto, Vice President, Shared R&D Core IP Division at Renesas. “Where most IP vendors offer only individual IP cores, we are providing developers access to rich IP solutions that includes proven CPUs and peripheral IPs. The introduction of the new IP Utilities opens up opportunities to create new IP markets and further expand our business that benefit from our extensive experience in semiconductor design.”

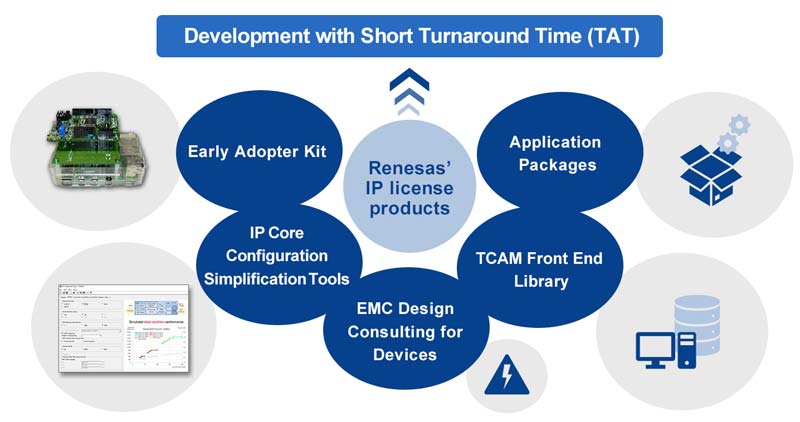

The new IP Utilities offerings include:

- Application packages that allow development of original microcontroller (MCU) with a short turnaround time (TAT)

Developers can take advantage of the application packages to implement application-specific functions as part of MCU development. For example, the 12-Axis Motor Control Package allows MCU developers to implement multi-axis motor control, which can be difficult to support in general-purpose MCU products. The base package includes a CPU, peripheral IPs, and motor control IPs, all capable of 12-axis stepping motor control. Developers may customize the system as desired, for example changing the number of axes, switching to brushless DC motor control or switching to a different CPU. - Early adopter kit enabling early evaluation of AI accelerator cores

Renesas’ early adopter kit allows developers to promote early phase evaluation of the Processing-in-Memory (PIM) AI accelerator IP (Note 1), which achieves superior power efficiency of 8.8 TOPS/W. Support is also available for software development. Developers can use the Raspberry Pi control board to combine PIM functions in a stacked configuration of up to three boards – expanding the scale of inference processing. - IP core configuration simplification tools

Developers can use the new configuration tools to study the specifications of complex IP cores with advanced functionality and optimize their performance in user applications. The first configuration tool is for the PCI Express controller core and enables the user to easily perform simulations involving variables, such as transfer speed, number of lanes, and bus bit width, and easily select the optimal configuration for achieving target performance from over 500,000 variations. - TCAM front end library to study product specifications

Renesas offers a front-end library for the Ternary Content Addressable Memory (TCAM) IP that combines advanced functionality and power efficiency. In addition to the conventional network packet processing field, developers can research new solutions with utilized trial TCAM front-end libraries in user-defined configurations including advanced technologies, such as the 7 nm process. - Equivalent EMC design consulting for devices

The IP Utilities offering includes EMC design consulting based on Renesas’ extensive experience of EMC design work in Renesas devices. By considering EMC design issues upstream in the system development process, for example with regard to pin assignments, board design, and component layout, developers can reduce the burden of noise-countermeasure following manufacture and reduce the iterations to fix.

Renesas plans to expand its lineup of IP Utilities with future offerings such as an evaluation environment for immediate evaluation of Ethernet TSN performance and an evaluation board mounted with an FPGA incorporating CPU cores.

For more information, visit https://www.renesas.com/products/ip-products.html

Note 1: The PIM IP is scheduled for release in 2021.

Renesas Electronics Corporation