Electric motors collectively consume a substantial portion of global electricity. According to the research firm IHS Technology, 96 percent of a motor’s lifetime costs are represented by pure electricity costs. Regulators have imposed more stringent energy standards for them, and manufacturers are scrutinizing their sizable contribution to equipment total cost of ownership (TCO). This has led to more complex motor control designs that use sensor-based and sensorless feedback loops and advanced algorithms for more precise control and greater motor efficiency.

Authors:

Jason Chiang, Sr. Marketing Manager, Industrial and

Ted Marena, Director, FPGA/SoC Marketing, with Microsemi (www.microsemi.com)

Motor designers also must support changing industrial control standards and technologies while providing critical system features that ensure safety, scalability and reliability. Meeting the twin goals of energy efficiency and enhanced system-level capabilities requires adequate processing power for algorithm processing along with flexible and scalable system architectures. Non-volatile, secure and low-power flash-based system on chip (SoC) FPGAs meet both challenges by delivering the necessary horsepower with a combination of both inherent and layered security and reliability with protected communications for Internet of Things (IoT) applications, and the ability to quickly and easily scale from small-footprint to feature-rich custom motor designs in a variety of multi-axis or high-RPM applications.

The Challenges

While traditional designs use simple scalar control, high-efficiency motors use Field-Oriented Control (FOC) across all torque and speed ranges to significantly improve efficiency. Because it is current-controlled, FOC also optimizes power-inverter circuitry and the motor footprint depending on application requirements. It uses feedback looping, with or without sensors, and sophisticated algorithms to regulate key motor behaviors including speed, position or angle, torque, current, and flux. While microcontrollers (MCUs) and DSPs have traditionally been used for algorithm processing in single- and dual-axis designs, their processing capabilities aren’t keeping up with growing multi-axis or high-rotation motor performance demands. Adding to the challenge, motor control efficiency is rarely the only concern, especially in connected factories where today’s Internet of Things (IoT) environment poses critical requirements for secure communications – something that flash-based FPGA architectures are ideally suited to address.

On the power electronics side of motor control designs, there is also a migration from insulated-gate bipolar transistor (IGBT) devices to silicon carbide (SiC) power MOSFET devices. SiC solutions provide higher bandgap for improved cooling (and therefore enable the use of smaller and cheaper heat sinks), greater thermal conductivity to drive higher power densities, and higher switching frequencies (greater than 100kHz) which result in smaller magnetics at the inverter stage. This, in turn, contributes to lowering the customer’s TCO.

On the control side, higher switching frequencies are where DSPs and MCUs don’t fare well. Some DSPs may optimize a few channels for high-frequency switching, but they still lack the ability to quickly adapt to changing requirements, and to add more pulse width modulation (PWM) channels to control the power electronics stage (in fact, this is often offloaded to an FPGA). ASICs and ASSPs have the same flexibility and scaling challenges.

Flash-based FPGAs offer greater performance than MCU/DSP-based solutions for high-speed, low-latency algorithm processing, while enabling the integration of additional system functionality to further improve TCO. Designers can use the flash-based FPGA to go beyond what MCUs/DSPs can support when scaling to higher switching frequencies and more PWM channels to match the power electronics.

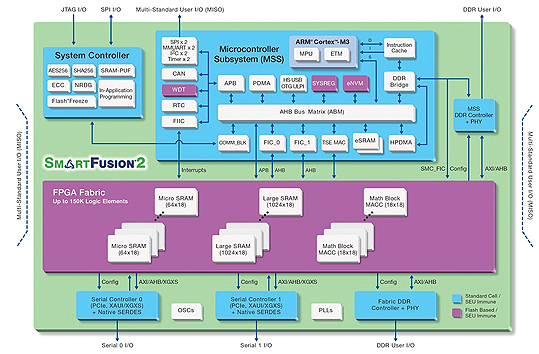

Figure 1 shows a solution where a flash-based SoC FPGA with an ARM® Cortex-M3 microcontroller can be used for motor control and monitoring functions. The FPGA fabric is used for hardware acceleration of motor control functions to improve performance, and for design flexibility. Motor control algorithms can be offloaded to the FPGA for faster parallel processing, with intelligent partitioning to ensure that all communications protocols in the microcontroller subsystem can be handled with zero impact on the motor control algorithm calculations that are running in the FPGA.

Capping off today’s FPGA solutions are modular suites of plug-and-play IP blocks tailored for implementing all necessary mathematical motor models. Developers can determine which IP blocks to hardware-accelerate in the FPGA fabric so they can meet the full range of algorithm processing challenges. These solutions ensure low-power operation while enabling developers to optimize their systems for reliability, safety and security using a simplified design process that speeds time to market while providing the flexibility and scalability to meet evolving needs.

Low-Power Operation

FPGAs used for motor control design must reduce both static and total power, especially at high frequencies and temperatures. FPGAs that feature an embedded single-transistor flash cell offer an advantage as compared to alternatives that use a six-transistor SRAM cell that must be configured from an external ROM during power-up. The latest flash-based FPGA solutions also use a comprehensive approach to minimizing power that encompasses process technology, architecture and the design of configurable logic, as well as embedded features including a hardened M3 MCU, 5G SERDES, DDR2/3, TSE, DSP blocks, and special power modes. This approach results in 50 percent lower total power and 10 percent lower static power than SRAM-based FPGA solutions.

Reliability, Safety and Security

In general, an FPGA is more reliable than a microcontroller for implementing motor control and network functions where deterministic timing is important. While there can be milliseconds of timing variability in a microcontroller, there are a few nanoseconds or less in the FPGA.

The best choice for security is flash-based, rather than SRAM-based FPGAs, because they store configuration information on-chip in non-volatile memory – the bit stream is never exposed at start-up. They also provide immunity to single event upsets (SEUs) that change configuration SRAM contents. Some flash-based FPGAs can also serve as root-of-trust devices with key storage capability to protect hyperconnected industrial IoT systems from cloning, tampering and other malicious attacks. These FPGAs address security needs with features like a physically unclonable function (PUF) from which the Private Key in a Public/Private Key scheme can be derived for implementing M2M authentication using Public Key Infrastructure (PKI). Other features include cryptographic accelerators, a random number generator, hardware firewalls to protect CPU/DSP cores, and Differential Power Analysis (DPA) countermeasures that, together, allow security to be layered as needed throughout the system to protect the hardware and data.

Design Simplicity through A Modular Approach

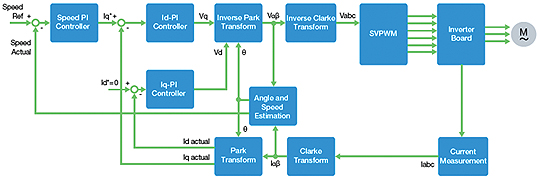

Modular and performance-oriented IP block suites enable algorithms to be implemented with plug-and-play simplicity. Designs can easily be ported across multiple platforms to speed time to market. All IP blocks are tested in simulations on actual hardware to ensure precise torque output, and easily integrated to create task-specific modules. Each block facilitates sharing of common FPGA resources for the most efficient chip utilization (see Figure 2).

The IP suite also includes all basic building blocks, including Clarke and Park transformations, proportional integral (PI) controllers for control loop feedback, and space vector PWM (SVPWM).

Flexibility and Scalability

A modular IP suite also simplifies customization and scaling to support different combinations of multi-axis motors or high-RPM solutions, while meeting evolving regional technology standards. The more compact the IP blocks (i.e., less than 10,000 logical elements for the entire suite), the more headroom there is to support integration needs.

An IP suite running on an FPGA can be scaled to drive from two brushless DC (BLDC)/stepper motor channels to a six-axis solution, or to extend motor performance beyond 70,000 RPM, depending on requirements. One way to scale to multi-axis FOC control is to time-division-multiplex each FOC loop within the device so each of the motors can be individually controlled for different reference speeds and torque requirements. Everything is implemented in the FPGA fabric, leaving the microprocessor subsystem available for running a communication protocol stack, providing the human-machine interface, or other tasks.

Designers of electric motors must meet energy mandates while ensuring systems can scale and adapt. Flash-based SoC FPGAs provide an increasingly attractive alternative to DSPs, MCUs, ASICs and ASSPs, combining the necessary processing horsepower with hardware and software programmability plus broad options for accelerating and intelligently partitioning functionality. Flash-based FPGAs add the benefit of inherent security, and can serve as the root of trust for secure IoT communications in the connected factory ■

www.microsemi.com