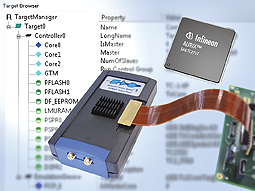

As a result of the very early and close cooperation with Infineon Technologies and several key customers, PLS now presents the first optimized test and debug solution, the Universal Debug Engine (UDE) 3.3, for the new multi-core architecture of the 32-bit microcontroller family AURIX. The first AURIX architecture based microcontroller (MCU), part number TC275T, contains three TriCore processor cores (version 1.6). Two of these are optimized for maximum performance (high-performance TriCore CPU 1.6P) and can execute up to three instructions in one cycle at a maximum clock frequency of 200MHz. With the third core, a high-efficiency TriCore CPU 1.6P, lowest possible power consumption and an efficient data exchange with the peripherals are the most important factors. It can execute a maximum of one instruction per cycle and is currently clocked at a maximum of 200MHz. The UDE 3.3 allows management and control of the various TriCore-CPUs within one user interface. This is supported by a flexible multicore program loader that enables the loading of program code and data as well as symbol information separately for each core.

PLS Programmierbare Logik & Systeme

www.pls mc.com